资讯

- 资讯

- 安检商家

艾崴安检机是如何高速的采集X光立体透视图像数据的?

2017-04-26 09:43:37 来源:

[摘要]对于艾崴100100客运站全功能型X光安检机来说,要高速扫描采集出高清的X光透视画面,就需要X光射线源与X光探测器即时的上电,并通过FPGA图像数据传输板准确地与工业控制计算机的CP

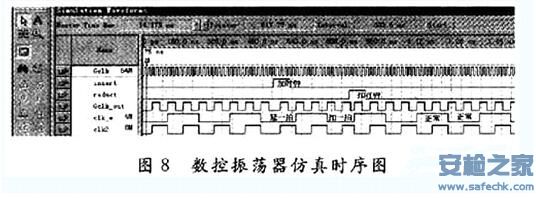

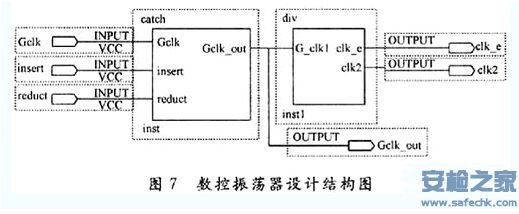

从该时序图可以看到,在insert与reduct信号的控制下,模块内部进行加/减时钟操纵,终极在输出时钟信号中得到延时或者扣除节拍的捕捉效果。

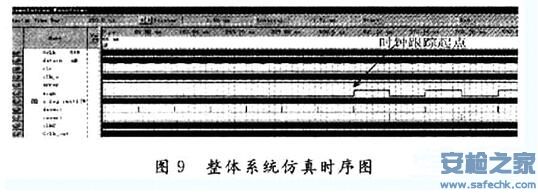

3 本系统整体时序仿真结果

结合安检机控制信号的实际传输情况,确定设计要求,对整体系统进行时序仿真。其中,选定Gclk频率为64 MHz,数据速率为4 Mb/s,并设定初始状态中,估计时钟和数据的相位差为103.775 ns,显示结果为相位滞后。根据数字锁相环的基本原理,必须进行扣脉冲的操纵后才能终极提取到同步时钟。鉴于该系统需要的捕捉精度较高,因此捕捉时间较长,并且由于整个仿真界面有限,只能观察到时钟提取过程,具体如图9所示。

由图9可以看出,从箭头处开始,出现了扣脉冲和加脉冲循环出现的情况,对于该情况分析如下:

由于初始设定的估计时钟相位滞后为103.775 ns,从图9仿真结果可以看出,在经历了7次扣脉运算后,由于每次扣脉冲的时间是1/(64×106)=15.225 ns,那么7个扣脉冲的时间就是15.225 ns×7=106.575 ns。在7个时钟扣除以后,相位又超前了106.575-103.775=2.8 ns,因此后续的操纵必须加脉冲,从而实现相位捕捉。由于每加一个脉冲是15.225 ns,之后会再次出现相位滞后,又进行扣脉冲操纵。如此循环,直到终极接近极限,提取到稳定的时钟信号。

4 X光安检机FPGA传输板硬件测试

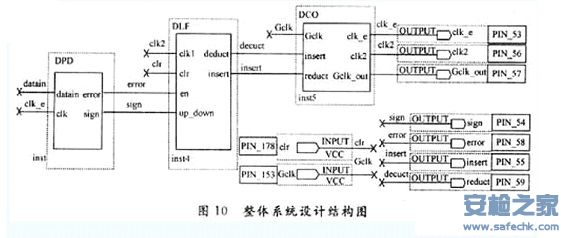

鉴于艾崴IWILDETECTOR X光安检机FPGA传输板系统应用于X光安检机控制信号传输系统中,故将该设计通过FPGA硬件平台进行了验证。该验证平台基于Altera公司Cyclone系列的EPlCl2Q240C8型号的FPGA芯片。鉴于实际系统中FPGA的本地系统时钟为32.768 MHz,故测试输进数据(datain)的速率为4.096 MHz。基于FPGA开发软件Quartus实现的测试系统整体结构图如图10所示。

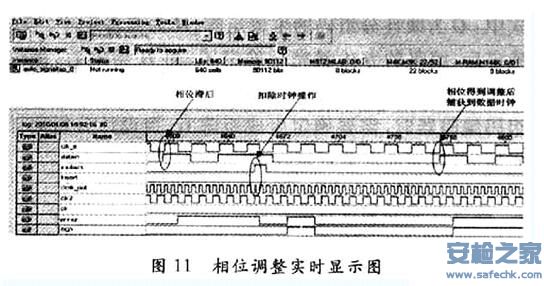

Signal TapⅡ逻辑分析器是Quartus软件中集成的一个内部逻辑分析软件,使用它可以观察设计的内部信号变化,为FPGA设计的调试、开发带来极大的方便,实用性很高。以下各图为Quartus软件中SignalTapⅡ实时观察到的数据。

相位调整验证如图11所示。由图11可以发现,开始时钟的相位滞后于数据相位。因此经过调整,通过数字环路滤波器输出的reduct信号控制数控振荡器模块进行扣时钟操纵,终极使本地估算时钟与数据时钟同步,正确地调整了相位。

相位调整验证如图11所示。由图11可以发现,开始时钟的相位滞后于数据相位。因此经过调整,通过数字环路滤波器输出的reduct信号控制数控振荡器模块进行扣时钟操纵,终极使本地估算时钟与数据时钟同步,正确地调整了相位。

十二当该系统捕捉到数据时钟后,就会稳定输出与数据信号同相的时钟信号,稳定状态截图如图12所示。

十三利用FPGA开发平台所具有的Signal TapⅡ功能,成功地在硬件平台上验证了该系统的可行性与稳定性。

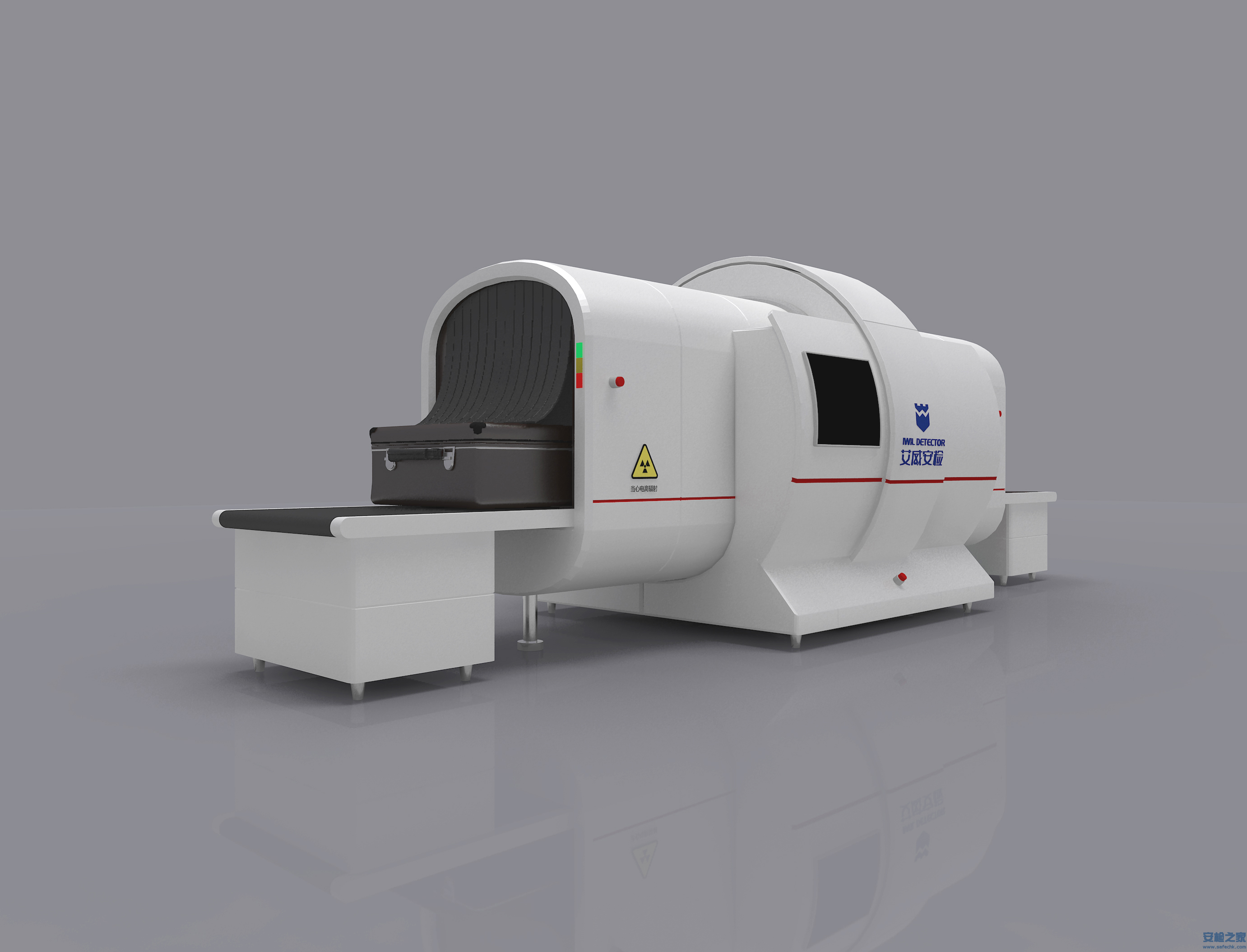

推荐产品

IWILDT™ AN-48002800L物流园大型货车X光安检系统

IWILDT™ AN-48002800L物流园大型货车X光安检系统价格:¥0.00

IWILDT™ AN-9000CTL静态立体断层扫描X光安检机

IWILDT™ AN-9000CTL静态立体断层扫描X光安检机价格:¥0.00