资讯

- 资讯

- 安检商家

艾崴安检机是如何高速的采集X光立体透视图像数据的?

2017-04-26 09:43:37 来源:

[摘要]对于艾崴100100客运站全功能型X光安检机来说,要高速扫描采集出高清的X光透视画面,就需要X光射线源与X光探测器即时的上电,并通过FPGA图像数据传输板准确地与工业控制计算机的CP

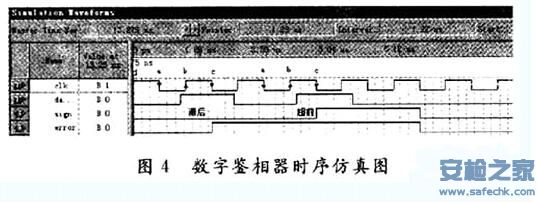

通过期序图可以看到,输进数据datain在本地估算时钟的边沿(包含上升沿和下降沿)触发下,依次存进寄存器a,b,c中。在时钟下降沿的触发下,通过对a,c信号进行异或运算,天生error信号,作为误差跳变尽对值输出。通过对b,c信号进行异或运算,天生sign信号,作为超前/滞后标志位输出。具体仿真结果如图4所示。

从图4可以发现,对于error信号,若前一位数据存在跳变,则输出高电平,否则输出低电平。对于sign信号,当估算时钟超前时,输出高电平,滞后时,输出低电平。该模块输出的两路信号将作为环路滤波器的输进信号,对下级结构进行控制。

2.2 数字环路滤波器

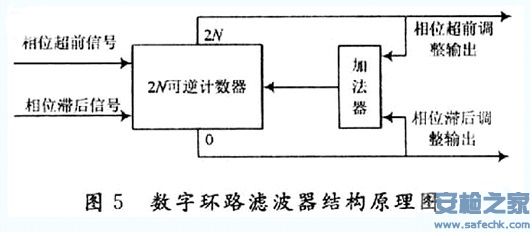

数字环路滤波器在锁相环路系统中主要起两种作用:其一,输出超前调整信号及滞后调整信号,以控制数控振荡器模块,对估计时钟进行相位调整;其二,有数字滤波作用,对噪声信号及高频干扰信号起到较好的抑制作用。数字环路滤波器内部拥有容量为2N的计数器,能够有效消除随机出现的具有正态分布特性的噪声信号。容量2N值越大,对噪声抑制效果越好,但同时2N值越大,跟踪速度越慢,实时捕捉能力下降。所以设计时,2N值的选取要综合考虑安检系统的实际参数要求。出于减少占用X光安检机FPGA系统资源的考虑,该系统采用随即徘徊滤波器作为实现方案。该滤波器原理框图如图5所示。

在实现方案中,环路滤波器通过加减计数逻辑单元实现。通过读取鉴相单元输出的两路使能信号对计数器进行代数累加或累减操纵,当达到记数的边界值0或2N时在输出端送出insert(插进时钟周期)或deduct(扣除时钟周期),与此同时,计数器内部寄存器值从2N自动恢复到N,重新开始。

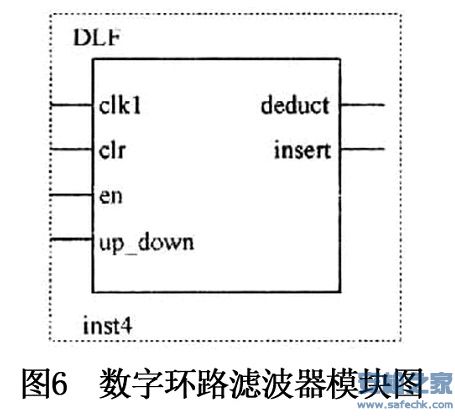

该模块如图6所示,其中clkl是记数时钟,由数控振荡器模块内部分频得到;clr是启动清零控制端;en接前端模块的error信号,该引脚是对记数功能的使能,即在输进数据(Data_in)有跳变时,才能判定相位误差;up_down是加减记数输进,与上级模块的sign使能信号相连,当sign=1时,做累加操纵,当sign=0时,做累减操纵,直到代数累加/累减运算到0或2N时,再对累加/累减计数器进行恢复。

catch模块的功能如下:

在IWILDETECTOR系统中,X光安检机FPGA传输板上用于驱动高速采样数据发送的主时钟为64 MHz,因此本设计中的全局时钟Gclk频率为64 MHz,这样可以有效节约X光安检机FPGA传输板上的硬件PLL资源,进步了硬件使用效率。

在catch模块内部,首先对全局时钟Gclk进行4分频,由于Gclk的设计频率为64 MHz,实现4分频后达到16 MHz。之后,catch模块根据前端环路滤波器的输出信号insert和reduct,在分频后的16 MHz时钟推动下,若insert信号出现高脉冲,自动在4分频后的时钟上补充一个Gclk时钟周期的延时,该操纵仅对insert信号的高脉冲上升沿有效;相类似,若reduct信号出现高脉冲,自动在4分频后的时钟上扣除一个Gclk时钟周期。

div模块的功能如下:

该模块为catch单元的后级,其主要功能是根据catch给出的Gelk_out信号进行N分频。在本系统中,需要恢复频率为4 MHz的数据时钟,因此这里第一个分频系数N=4,输出为1*=4 MHz的时钟信号(clk_e),第二个分频时钟为数字环路滤波器的记数时钟,该信号是经过2分频(频率为8 MHz)后的时钟信号,用于进行DLF滤波。与此同时,也可以加速该时钟,这样可以缩短捕捉时间,并且扩展其捕捉带宽。该数控振荡器的加扣时钟和分频的综合仿真时序图如图8所示。

推荐产品

IWILDT™ AN-48002800L物流园大型货车X光安检系统

IWILDT™ AN-48002800L物流园大型货车X光安检系统价格:¥0.00

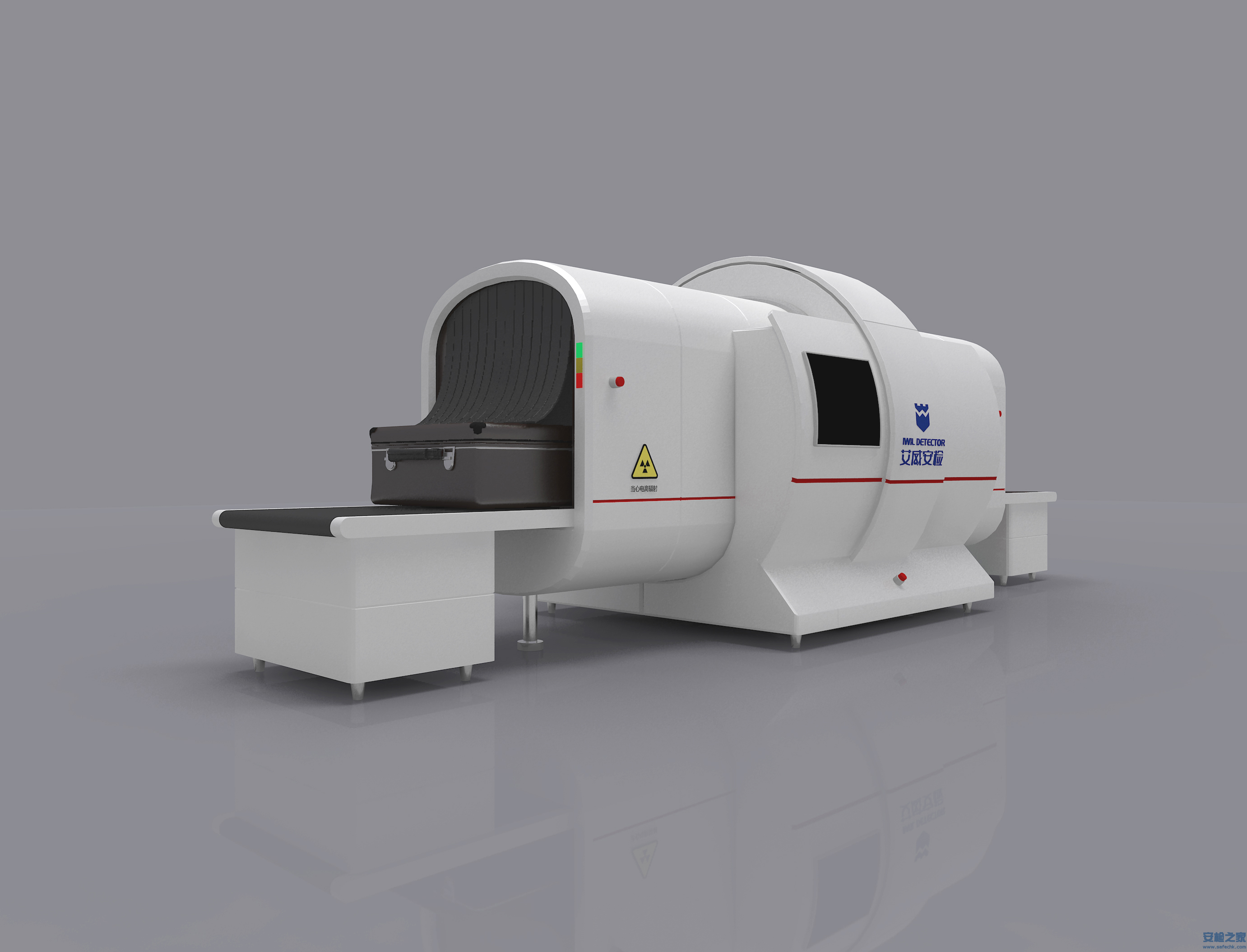

IWILDT™ AN-9000CTL静态立体断层扫描X光安检机

IWILDT™ AN-9000CTL静态立体断层扫描X光安检机价格:¥0.00