资讯

- 资讯

- 安检商家

世界首个RISC-V区块链芯片即将开发,欲打造《终结者》中的天网工程!

2018-08-07 14:53:49 来源:

[摘要] 不久前才成立的非营利组织OpenSingularity基金会(OpenSingularity Foundation)宣称即将开发出世界上第一款区块链(blockchain)芯片以及超可扩展的区块链物联网(IoT)网路,从

Skynet计划最初将针对整合来自Arm的处理核心,包括低功耗嵌入式应用的Arm Cortex-M系列处理核心,以及高端应用的Arm Cortex-A 64位高性能处理器系列,以实现低功耗和小占位面积。该生态系统还提供了先进的微控制器(MCU)汇流排架构(AMBA),以互连多个周边设备(IO、协同处理器和记忆体控制器等)。此外,多家供应商可为各种制程节点提供可靠的周边设备。

一开始,透过Arm的广泛渗透也很重要,因为它提供了一个经验证的社群,可支持开机加载程序等整个软件堆叠、核心、驱动程序、工具库、应用和软件开发工具等,如编译器、分析器和除错器。

尽管如此,OpenSingularity表示,随着RISC-V开源指令集架构(ISA)日益成熟,该公司正致力于为开发基于此ISA的客户定制处理器探索其他替代方案以及周遭生态系统。该公司表示,相较于Arm处理器(BOOMv2 vs ARM Cortex-A9),RISC-V核心的最新架构显示可实现更小芯片尺寸与更高性能的理想结果。

OpenSingularity在其论文中评论说:「RISC-V可提供取代Arm的理想替代方案,带来一个极具成本效益的Skynet核心,因为它无需像Arm一样的授权费用,这种节省成本的作法可望造福SoC制造商并成为加速其采用的动力。我们将监控RISC-V生态系统扩展的进展,并决定哪一款CPU核心可作为Skynet核心的基础。

该公司还计划透过与SoC制造商合作,依据特定应用的需求开发整个整合堆叠,从而加速开发完整的软件堆叠。

Arm vs. RISC-V架构

该基金竭尽全力地为其区块链IoT芯片评估Arm与RISC-V架构的特性。

采用RISC架构的Arm旨在实现固定长度、简单但功能强大的指令,以高时脉速度执行单个周期。该架构基于许多原则,以实现简单的设计和快速的时脉速率。管线设计在一个阶段中解码而无需要微码(microcode),并为快速执行指令定义了大量的通用暂存器。Arm采一种资料处理指令仅适用于暂存器的加载/储存架构,而加载/储存方案则用于从记忆体传输资料。

然而,这与纯粹的RISC存在一些差异。Arm的某些指令采用可变周期执行,例如多暂存器加载/储存,以实现更快和更高的程序代码密度。内建桶式移位器可提高性能和代码密度,但也导致了更复杂的指令。Thumb 16位元指令集可以提高约30%的程序代码密度。条件执行透过减少分支以提高性能和程序代码密度,并为DSP操作添加了一些增强指令。

该基金会并补充说,现有的ISA,如x86/x64,是专有且非常复杂的,但其细节经常隐藏在冗长的手册中,ISA的一些细节其甚至根本没有公开。此外,广泛使用的ISA已存在多年,而且其设计经常被延用,以支持后向相容性。专有的ISA由英特尔(Intel)和Arm等公司实体所拥有、管理和控制。

为了解决这些问题,加州大学柏克莱分校提出了RISC-V计划。RISC-V采用的开放来源途径意味着许多不同的公司可以提供RISC-V架构的硬件方案。建立一个让多家供应商可以竞争建置单一ISA的生态系统,可望带来许多好处,这些在其他开放来源计划中可见一斑。OpenSingularity补充说,RISC-V旨在建立一个现代的ISA,其中包含处理器设计的最新想法。现代ISA力求比传统的ISA更精简、更实用,而且还能适应快速的硬件建置。

它认为,IoT应用中的许多嵌入式处理器需要的是便宜、可靠且简单,但不一定要求速度、支持作业系统、多核心或支持64位元操作。另一方面,它还发现有一些应用也需要具有多核心和64位元操作的处理器。

OpenSingularity之所以选择RISC-V是因为它能够在ISA中加进一些选项,以实现各种设计选择。在这方面,该基金会补充说RISC-V实际上并不是单一的ISA,而是更多相关ISA的组合。

RISC-V提供了三种基本整数ISA:RV32I、RV64I和RV128I,分别用于32位元、64位元和128位元位址宽度。为硬件整数作业提供了40个固定32位元宽度的指令,以及几个标准扩展,包括一个仅有16个暂存器的嵌入式处理器。

压缩的指令集将常规的32位元指令压缩为16位元,类似于Arm针对嵌入式应用的Thumb指令集,这将有助于缩减程序代码的大小,以提高处理器性能——因为它允许更多指令快取,因而缩减了从主处理器获取指令的时间(这部份通常造成性能瓶颈)。

推荐产品

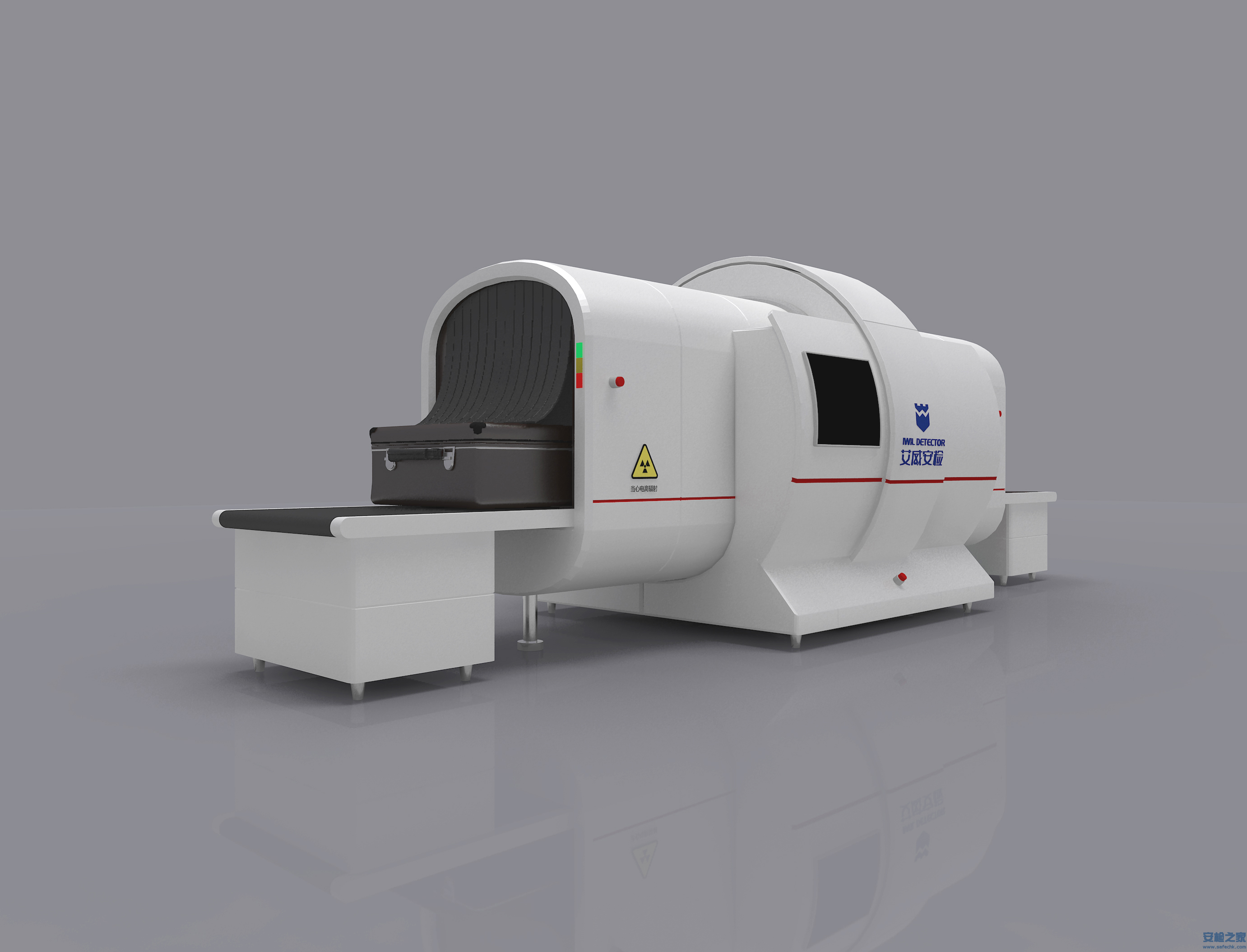

IWILDT™ AN-48002800L物流园大型货车X光安检系统

IWILDT™ AN-48002800L物流园大型货车X光安检系统价格:¥0.00

IWILDT™ AN-9000CTL静态立体断层扫描X光安检机

IWILDT™ AN-9000CTL静态立体断层扫描X光安检机价格:¥0.00